# Iterative Compilation and Performance Prediction for Numerical Applications

Grigori G. Fursin

Doctor of Philosophy

Institute for Computing Systems Architecture School of Informatics University of Edinburgh

2004

### Abstract

As the current rate of improvement in processor performance far exceeds the rate of memory performance, memory latency is the dominant overhead in many performance critical applications. In many cases, automatic compiler-based approaches to improving memory performance are limited and programmers frequently resort to manual optimisation techniques. However, this process is tedious and time-consuming. Furthermore, a diverse range of a rapidly evolving hardware makes the optimisation process even more complex. It is often hard to predict the potential benefits from different optimisations and there are no simple criteria to stop optimisations i.e. when optimal memory performance has been achieved or sufficiently approached.

This thesis presents a platform independent optimisation approach for numerical applications based on iterative feedback-directed program restructuring using a new reasonably fast and accurate performance prediction technique for guiding optimisations. New strategies for searching the optimisation space, by means of profiling to find the best possible program variant, have been developed. These strategies have been evaluated using a range of kernels and programs on different platforms and operating systems. A significant performance improvement has been achieved using new approaches when compared to the state-of-the-art native static and platform-specific feedback directed compilers.

## Acknowledgements

I would like to thank my supervisor Dr. Michael O'Boyle for the overwhelming support during all the hard years of this research and for providing a great working environment. I would also like to thank Prof. Nigel Topham for his important guidance at the beginning of the project, Prof. Olivier Temam, Dr. Peter Knijnenburg and members of the MHAOTEU project for the collaboration and fruitful discussions.

I am grateful to Monika, Dyane and Margaret for their great administrative support.

I would like to thank Shun, Bjoern, Tom and Tim for the interesting discussions during lunch breaks.

I am grateful to all my friends who helped me to switch off my work occasionally and relax, particularly to Viki, Laura, Ernest, Joe, Annemieke, Pille, Paulo, Aghlab, Gaurav, Melissa, Hachemy, Katarina, Ghassan, Takeshi, Emilio, Atif, Yannos, Lucia and all my partners in sport activities.

Finally, special thanks to Eglantine and Georgios for keeping me out of the misery during difficult times, and to my parents and brother Leonid for the moral support.

# **Declaration**

I declare that all the research and developed software presented in this thesis is my own, unless stated otherwise in the text. Some of the material used in this thesis has been published in the following papers:

- [FOT<sup>+</sup>04] G. Fursin, M. O'Boyle, O. Temam, and G. Watts. Fast and accurate method for determining a lower bound on execution time. *Concurrency Practice and Experience*, 16(2-3), pages 271-292, 2004.

- [FBK03] G.G. Fursin, M.F.P. O'Boyle, and P.M.W. Knijnenburg. Evaluating Iterative Compilation. *Accepted for publication in "Springer Lecture Notes in Computer Science"*.

- [FBK02] G.G. Fursin, M.F.P. O'Boyle, and P.M.W. Knijnenburg. Evaluating Iterative Compilation. Proceedings of Languages and Compilers for Parallel Computing (LCPC'02), pages 305-315, 2002.

- [FOT<sup>+</sup>01] G. Fursin, M. O'Boyle, O. Temam, and G. Watts. Fast and accurate evaluation of memory performance upper-bound. *Proceedings of Compilers for Parallel Computers (CPC'01)*, pages 163-171, June 2001.

January, 2004

# Contents

| ABSTRACT                                | I     |

|-----------------------------------------|-------|

| ACKNOWLEDGEMENTS                        | II    |

| DECLARATION                             | III   |

| CONTENTS                                | IV    |

| LIST OF FIGURES                         |       |

| LIST OF TABLES                          | IX    |

| CHAPTER 1. INTRODUCTION                 | 1     |

| 1.1 The problem                         |       |

| 1.2 Contributions                       |       |

| 1.3 Thesis structure                    |       |

| CHAPTER 2. BACKGROUND                   | 6     |

| 2.1 Processor architecture              |       |

| 2.1.1 Processor design evolution        |       |

| 2.1.2 Pipelining                        | 9     |

| 2.1.3 Superscalar processors            |       |

| 2.2 Memory hierarchy                    |       |

| 2.2.1 Memory design evolution           |       |

| 2.2.2 Locality and cache design         |       |

| 2.3 Compiler technology                 |       |

| 2.3.1 Introduction to compiling         |       |

| 2.3.2 Code optimisations                |       |

| 2.4 Summary                             |       |

| CHAPTER 3. MEMORY HIERARCHY OPTIMISATIO | DNS25 |

| 3.1 Program transformations             |       |

| 3.1.1 Introduction                      |       |

| 3.1.2 Loop tiling                       |       |

| 3.1.3 Array padding                     |       |

| 3.1.4 Loop unrolling                    |       |

| 3.1.5 Other transformations             |       |

| 3.2 Static analysis and optimisations             |     |

|---------------------------------------------------|-----|

| 3.2.1 Improving ILP                               |     |

| 3.2.2 Data locality analysis and optimisations    |     |

| 3.2.3 Reducing conflict misses                    | 49  |

| 3.2.4 Reducing compulsory misses                  |     |

| 3.3 Dynamic analysis                              |     |

| 3.3.1 Profiling                                   |     |

| 3.3.2 Simulating                                  | 55  |

| 3.4 Dynamic optimisations                         |     |

| 3.4.1 Feedback-assisted and iterative compilation |     |

| 3.4.2 Adaptive compilation                        | 61  |

| 3.5 Summary                                       |     |

| CHAPTER 4. ITERATIVE COMPILATION                  | 63  |

| 4.1 Introduction                                  |     |

| 4.2 Experimental framework                        |     |

| 4.2.1 Software architecture                       |     |

| 4.2.2 Platforms and applications                  |     |

| 4.3 Impact of program transformations             |     |

| 4.3.1 Array padding                               |     |

| 4.3.2 Loop tiling                                 |     |

| 4.3.3 Loop unrolling                              |     |

| 4.4 Basic search strategy                         |     |

| 4.5 Experimental results                          |     |

| 4.6 Summary                                       | 91  |

| CHAPTER 5. PERFORMANCE PREDICTION                 |     |

| 5.1 Introduction                                  |     |

| 5.2 Motivation and example                        |     |

| 5.3 Performance prediction algorithm              |     |

| 5.3.1 Collecting data values                      |     |

| 5.3.2 Removing cache misses                       | 101 |

| 5.3.3 Preserving data dependences                 |     |

| 5.3.4 Ensuring correct code execution             | 103 |

|                                                   |     |

| 5.3.5 Array indirection and control flow |     |

|------------------------------------------|-----|

| 5.4 Implementation                       |     |

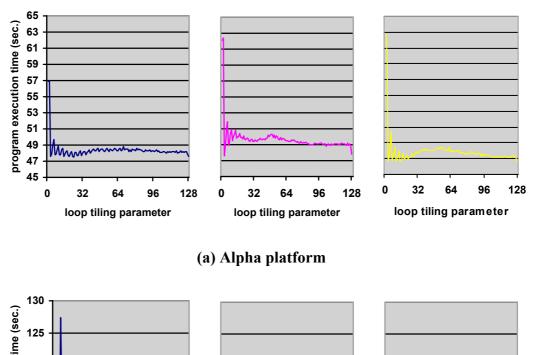

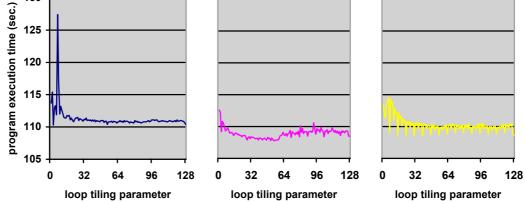

| 5.4.1 Alpha platform                     |     |

| 5.4.2 Pentium platform                   |     |

| 5.5 Experimental results                 |     |

| 5.6 Performance validation               |     |

| 5.7 Comparison with existing techniques  |     |

| 5.8 Summary                              |     |

| CHAPTER 6. SEARCH SPACE REDUCTION        | 118 |

| 6.1 Introduction                         |     |

| 6.2 Using performance prediction         |     |

| 6.3 Random search strategy               |     |

| 6.4 Experimental results                 |     |

| 6.5 Comparison with existing techniques  |     |

| 6.6 Using smaller dataset                |     |

| 6.7 Summary                              |     |

| CHAPTER 7. CONCLUSIONS                   | 140 |

| 7.1 Summary                              |     |

| 7.2 Critical review and future work      |     |

| APPENDIX A. DESCRIPTION OF PLATFORMS     | 143 |

| A.1 Alpha platform                       |     |

| A.2 Pentium platform                     |     |

| BIBLIOGRAPHY                             | 145 |

# **List of Figures**

| Figure 2.1: Von Neumann processor architecture                                       | 7  |

|--------------------------------------------------------------------------------------|----|

| Figure 2.2: Instruction execution on non-pipelined and pipelined processors          | 10 |

| Figure 2.3: Instruction execution on a pipeline when stall occurs                    | 11 |

| Figure 2.4: Memory hierarchy in current computing systems                            | 18 |

| Figure 3.1: Abu-Sufah's transformation of imperfectly nested loop to a perfect       |    |

| loop nest                                                                            | 29 |

| Figure 3.2: Data transformation theory examples                                      | 31 |

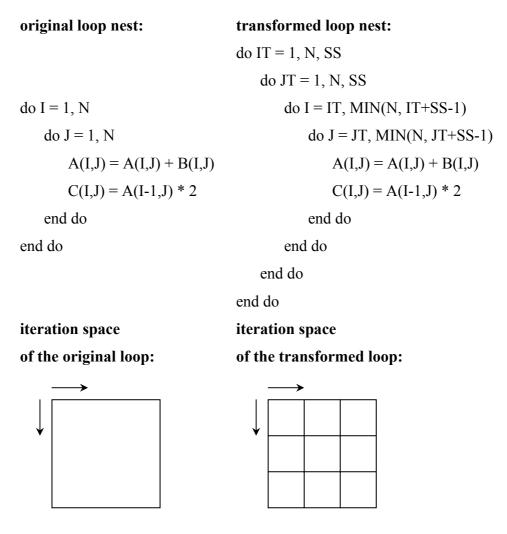

| Figure 3.3: Loop tiling example                                                      | 32 |

| Figure 3.4: Generalised version of loop tiling                                       | 33 |

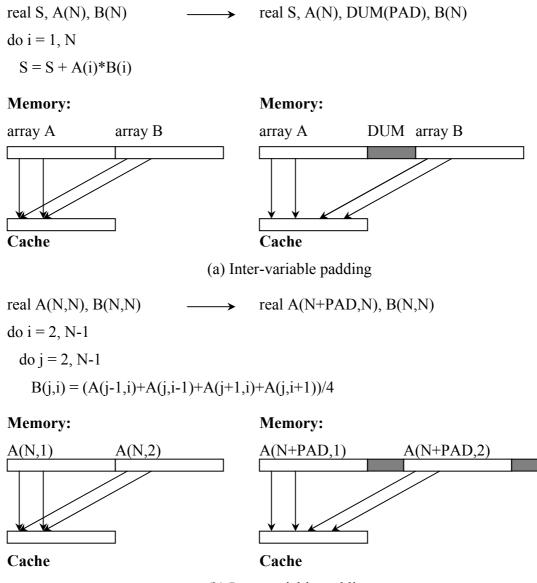

| Figure 3.5: Intra-variable and inter-variable array padding examples                 | 34 |

| Figure 3.6: Loop unrolling example                                                   | 35 |

| Figure 3.7: Generalised version of loop unrolling                                    | 36 |

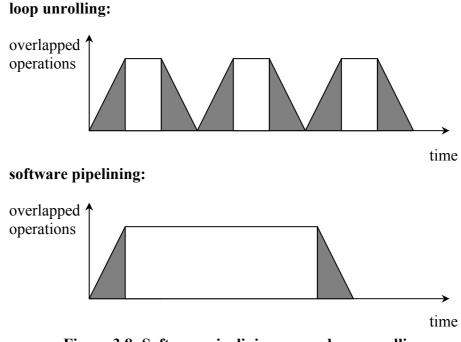

| Figure 3.8: Software pipelining versus loop unrolling                                | 38 |

| Figure 3.9: Software prefetching example for inner product calculation               | 39 |

| Figure 3.10: Unroll-and-jam transformation example                                   | 40 |

| Figure 3.11: Algorithm for calculating loop cost (McKinley et al.)                   | 46 |

| Figure 3.12: Loop cost for matrix multiplication kernel (McKinley et al.)            | 47 |

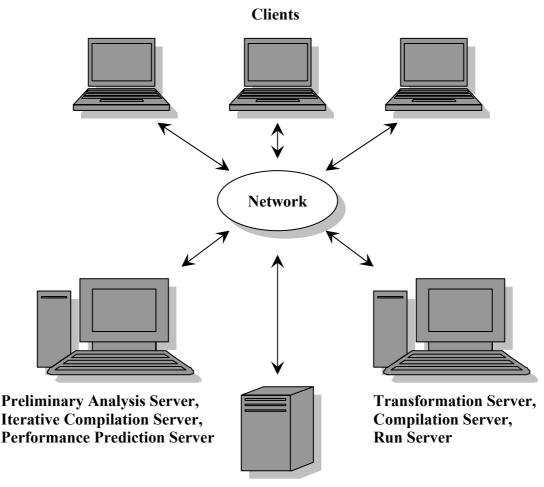

| Figure 4.1: Software architecture of the optimising suite                            | 66 |

| Figure 4.2: Source code of matmul and sor kernels                                    | 69 |

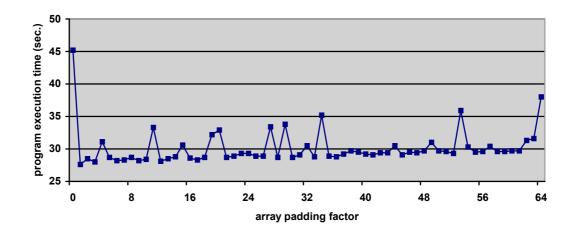

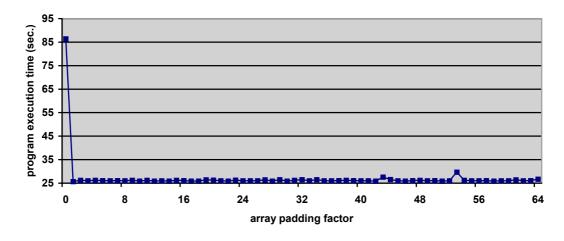

| Figure 4.3: Execution time for varying array padding factors (matmul)                | 71 |

| Figure 4.4: Execution time for varying array padding factors (swim)                  | 72 |

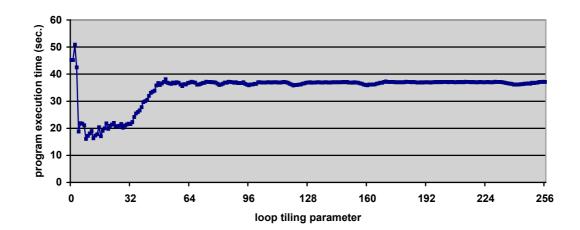

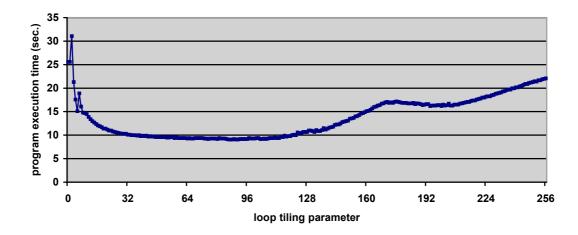

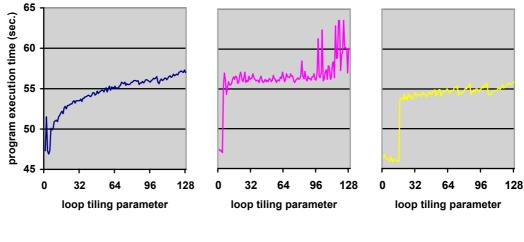

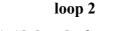

| Figure 4.5: Execution time for varying loop tiling factors applied to the most time  |    |

| consuming loop (matmul)                                                              | 74 |

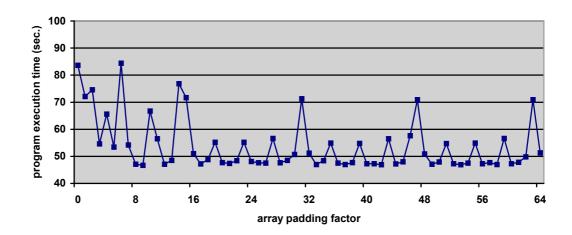

| Figure 4.6: Execution time for varying loop tiling factors applied to the three most |    |

| time consuming loops (swim)                                                          | 75 |

| Figure 4.7: Execution time for varying loop unrolling factors applied to the most    |    |

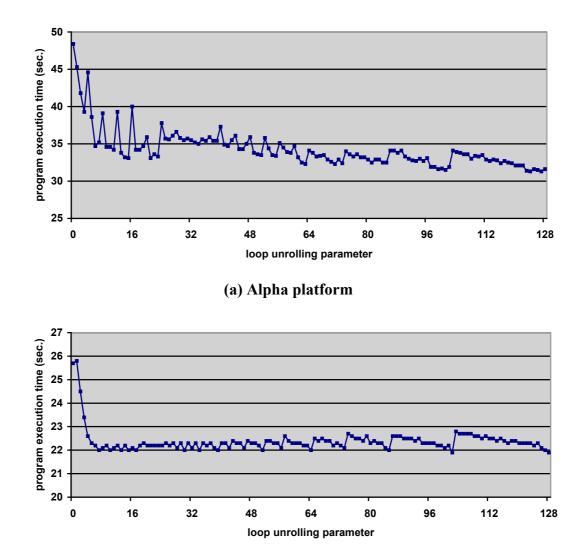

| time consuming loop (matmul)                                                         | 76 |

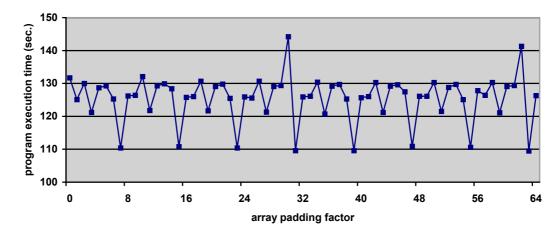

| Figure 4.8: Execution time for varying loop unrolling factors applied to the three   |    |

| most time consuming loops (swim)                                                     | 77 |

| Figure 4.9: Basic search strategy algorithm                                          | 79 |

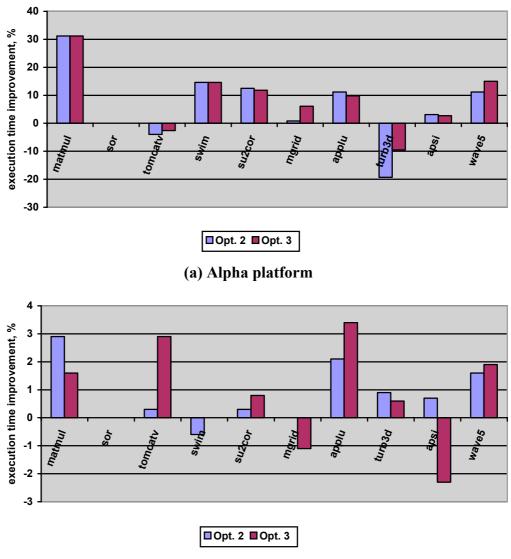

| Figure 4.10: Execution time improvements (%) of Opt.2 and Opt.3 over Opt.1          | . 85 |

|-------------------------------------------------------------------------------------|------|

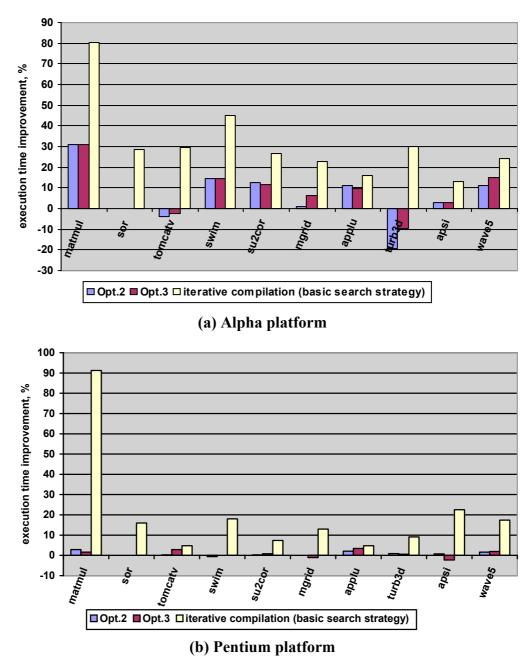

| Figure 4.11: Execution time improvements (%) after iterative compilation with       |      |

| the basic search strategy, Opt.2 and Opt.3 over Opt.1                               | . 88 |

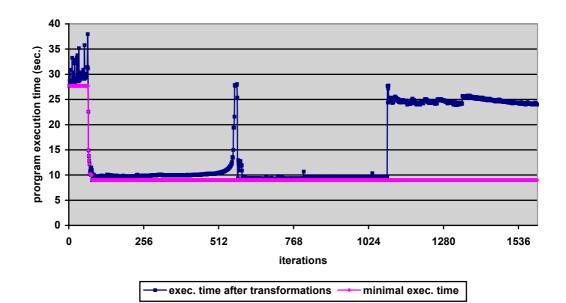

| Figure 4.12: Changes in execution time during each iterative step (matmul)          | . 90 |

| Figure 5.1: Assembler transformations to predict potential performance              | . 96 |

| Figure 5.2: Program modifications to ensure correct code execution after            |      |

| performance prediction transformation                                               | . 98 |

| Figure 5.3: Performance prediction algorithm                                        | 99   |

| Figure 5.4: Data collection for performance prediction transformation               | 100  |

| Figure 5.5: Performance prediction transformation algorithm for removing cache      |      |

| misses                                                                              | 101  |

| Figure 5.6: Algorithm to ensure correct execution of the transformed code           | 103  |

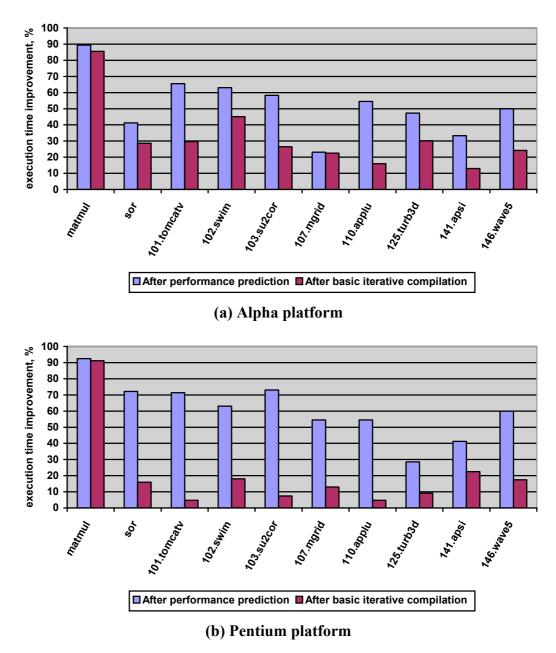

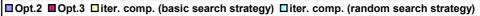

| Figure 5.7: Overall potential and iterative performance improvement (%)             | 111  |

| Figure 5.8: Original matmul and synthetically generated kernel                      | 114  |

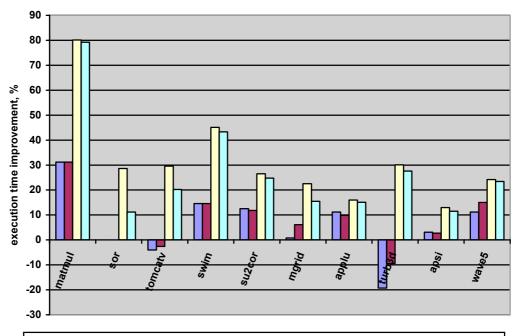

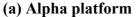

| Figure 6.1: Random search strategy algorithm                                        | 121  |

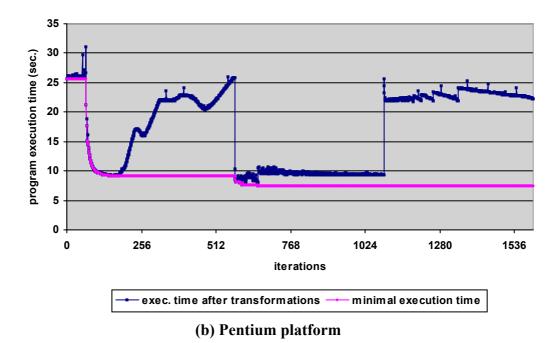

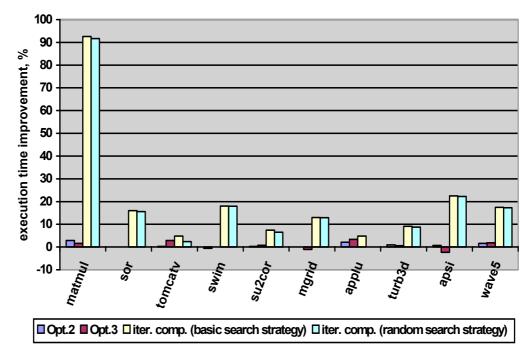

| Figure 6.2: Execution time improvements (%) after iterative compilation with the    |      |

| random search strategy and comparison with the basic search strategy                |      |

| and compiler optimisations                                                          | 128  |

| Figure 6.3: Algorithm to compute the best tile size that removes self-interferences |      |

| (Lam et al.)                                                                        | 131  |

| Figure 6.4: Algorithm to compute the best rectangular tile size (Coleman and        |      |

| McKinley)                                                                           | 132  |

|                                                                                     |      |

# **List of Tables**

| Table 4.1: Description of applications                                             | . 68 |

|------------------------------------------------------------------------------------|------|

| Table 4.2: Application execution times after internal compiler optimisations (best |      |

| times are highlighted)                                                             | . 84 |

| Table 4.3: Execution time improvements (%) after iterative compilation with the    |      |

| basic search strategy over Opt.1, Opt.2 and Opt.3                                  | . 87 |

| Table 5.1: Original and lower-bound execution times with IPCs (Alpha platform).    | 107  |

| Table 5.2: Original and lower-bound execution times with IPCs (Pentium             |      |

| platform)                                                                          | 108  |

| Table 5.3: IPC of the original and transformed programs obtained using the         |      |

| simulator with normal and perfect caches                                           | 113  |

| Table 5.4: Cache behaviour of the original and transformed programs                | 113  |

| Table 5.5: Example demonstrating the advantage of the proposed performance         |      |

| prediction technique over the existing ones that are based on counting             |      |

| the number of cache misses                                                         | 115  |

| Table 6.1: Example demonstrating the use of the performance prediction             |      |

| technique in iterative compilation (Pentium platform)                              | 119  |

| Table 6.2: Comparison of the basic and random search strategies (matmul,           |      |

| Pentium platform)                                                                  | 123  |

| Table 6.3: Total number of analysed loops and the number of selected loops for     |      |

| the random search strategy                                                         | 125  |

| Table 6.4: Execution time improvements (%) after iterative compilation with the    |      |

| random search strategy over Opt.1, Opt.2 and Opt.3                                 | 126  |

| Table 6.5: Execution time improvements (%) and number of iterations needed         |      |

| after iterative compilation with the random and basic search strategies            |      |

| over Opt.1                                                                         | 127  |

| Table 6.6: Comparison of tile size selection by 4 algorithms: Lam et al., Coleman  |      |

| and McKinley, iterative compilation with the basic and random search               |      |

| strategies                                                                         | 134  |

| Table 6.7: Execution time improvements (%) after static optimisation algorithms,   |      |

| after native compiler static and dynamic optimisations, after iterative            |      |

- Table 6.9: Comparison of performance improvements after iterative compilationwith the basic search strategy for matmul when the original andsmaller datasets are used during optimisation on the Alpha platform .... 137

- Table 6.10: Performance improvements after iterative compilation with the basic

search strategy for SPEC benchmarks when the training dataset is used

during optimisation and then the best optimisation is applied to the

reference data

138

# **Chapter 1**

# Introduction

This chapter briefly describes the research area, the contributions and the structure of this thesis.

### 1.1 The problem

Considerable progress has been made in processor technology in the last 30 years. Early processors were simple 4/8-bit in-order execution chips with working frequencies of several megahertz, supporting only direct-addressed memory of several hundred kilobytes. Currently, however, they are complex 32/64-bit devices working at gigahertz frequencies with the support of out-of-order parallel multiple instruction execution, value prediction, speculation and virtual memory support. The sole motivation behind these advances is to make the processor perform computations faster. Naturally, the amount of data to process has also grown. This data is kept in main memory and is accessed by the processor as and when needed.

One of the major problems in current computing systems is that the memory cannot supply data to the processor immediately on request due to its physical size and the speed of signal propagation. This leads to a mismatch between processor and memory performance. It was observed that while microprocessor performance has improved by approximately 55% per year since 1987, memory performance has only improved by 7% per year [HP96]. This leads to the processor-memory bottleneck; no matter how fast the processor is, the overall performance of the computing system is limited by the speed of memory.

The most common solution to this problem is based on the introduction of intermediate smaller, but faster layers of memory, known as cache memory, between the processor and main memory [Smi82]. Caches are designed to exploit program locality [MB76] and are based on the two following observations: a) a memory location recently referenced is likely to be referenced again soon and b) a memory location adjacent to a referenced location is likely to be referenced soon. In practice,

however, programs may not exhibit this property. In this case, the task of restructuring of the data layout in memory or transforming the program to exploit locality has to be performed either manually by the programmer or automatically by the compiler.

Modifying the program manually is tedious, time consuming and requires a good knowledge of the underlying hardware. Furthermore, if the program needs to be ported to a new platform, it has to be optimised once again to reflect the new hardware parameters, which may require many man-hours and hence is economically expensive. Conversely, compilers attempt to solve this problem by utilising static models of different platforms and transforming the code to match the particular hardware platform. Nevertheless, due to the complexity of the memory and processor architecture and for reasons of tractable analysis, compilers have to assume a significantly simplified machine model. In addition to this, the lack of important runtime information such as loop bounds and branches taken, means that compiler memory optimisations often fail to achieve performance improvements.

One of the techniques introduced to reflect the importance of run-time information is profile-directed compilation [PH90]. It is a dynamic optimisation process, which is performed in two steps. In the first step, the optimised program is instrumented and executed to collect certain run-time parameters. In the second step, the program is optimised according to the information obtained. Yet, most current profile-directed optimisations attempt to improve instruction cache use or enable better branch prediction whilst ignoring data cache usage, which may not improve the overall program performance if a memory bottleneck is present.

A further weakness of current techniques is the inability to determine the potential benefit from an optimisation. Performance prediction techniques are usually based on a simplified hardware model and are inaccurate, or based on simulators that are extremely slow, sometimes by several orders of magnitude in comparison with the original program execution time. Alternatively, hardware counters can be used, but they often mispredict performance on current superscalar out-of-order execution processors. For example, a program may generate many cache misses that will be detected by hardware counters. This will lead to an assumption that memory optimisations are beneficial for this program, but memory access delays may be

hidden by other calculations performed in parallel and in this case memory optimisations will fail in gaining performance. However, knowing the potential performance improvement before optimising the code is important for judging the amount of effort worth expending.

### **1.2 Contributions**

Three major contributions to the above problems are presented in this thesis. An iterative feedback assisted optimisation approach is presented. It is based on searching for the best possible program transformations in a large optimisation space. Unlike other search optimisation techniques that use some heuristics to analyse and optimise small kernels, it can successfully optimise large applications by applying transformations in a smart phase order to cut down the search space. This approach, while being slow and requiring thousands of runs of the transformed program, achieves a considerable performance improvement over state-of-the-art compilers. Considering that the set of transformations used in this approach is specially chosen to be the same or smaller than in used compilers, it demonstrates that current optimisers fail to find the best possible transformations statically.

A new performance prediction technique for estimating the lower bound on program execution time is then presented. This is a dynamic, reasonably fast and accurate approach, based on transforming all array references into scalar references to remove cache misses, and profiling the new code.

Finally, an approach for reducing the iterative compilation time dramatically is presented. It uses the performance prediction technique to detect sections of the program that may potentially benefit from optimisations and applies a random iterative transformation search to those sections. This can reduce the number of iterations by two orders of magnitude in comparison with the basic iterative search, thus making iterative compilation a superior and realistic option over the current static or profile-directed optimisations.

The developed techniques have been implemented inside a cross-platform toolset, evaluated on two distinct RISC and CISC platforms using a variety of kernels and benchmarks and compared with the current native state-of-the-art compilers.

### **1.3 Thesis structure**

This thesis has the following structure. Chapter 2 surveys various processor designs and advances in the semiconductor technology. It describes and analyses techniques for exploiting instruction level parallelism such as pipelining and multiple instruction issue with out-of-order execution. This chapter further presents the evolution of the memory hierarchy and describes various cache designs that exploit locality to reduce memory access time. It also contains an introduction to basic compilation and optimisation techniques.

Chapter 3 presents related work on memory optimisations. It starts with introducing formal notations for describing loops and data accesses, and then presents models to unify and ease program transformations and data locality analysis. This is followed by a description of various static methods for analysing and improving cache utilisation for a broad range of programs. This chapter concludes by presenting multiple dynamic techniques for profiling and optimising program performance.

Chapter 4 describes a new platform-independent iterative optimisation approach that is able to outperform current state-of-the-art commercial compilers with both static and feedback-directed optimisations enabled. This chapter analyses the influence of array padding, loop tiling and loop unrolling transformations on the program performance in detail, and examines the reasons why static optimisation approaches often fail in improving performance or can even degrade it. Experimental results show considerable performance improvements after using this iterative approach for two kernels and eight SPEC benchmarks on two platforms. However, the major drawback of iterative compilation is its excessive optimisation time. Thousands of executions of program variants are often needed, which may not be tolerable for general-purpose computing. Therefore, the two following chapters present techniques to reduce iterative compilation time.

Chapter 5 presents a new performance prediction technique that can provide information about whether program segments have the potential for performance improvement or not. This platform-independent technique transforms the original program at the assembler level in such a way that the new program behaves as if there were no cache misses occurring. Profiling the original and transformed programs and comparing the difference in the execution time shows the potential for performance improvement. This technique is reasonably fast and accurate as no simulations are involved and no approximations are used. It is compared to other existing methods and it is shown that many of these methods, which are based on counting the number of cache misses, give inaccurate predictions on modern superscalar processors with out-of-order execution. Performance prediction can reduce the iterative compilation search space by removing loop nests that do not have any potential for performance improvement from the search.

Chapter 6 presents a new iterative compilation approach that combines performance prediction and random search, thus considerably reducing the search space. Using this optimisation technique reduces the number of program executions to less than a hundred while still obtaining considerable performance improvement. This makes iterative compilation a realistic approach for general-purpose optimisation. A comparison with other techniques is presented at the end of this chapter. Finally, chapter 7 summarises the results achieved and outlines future work.

# **Chapter 2**

# Background

This chapter briefly surveys trends in processor design; describes memory design evolution and summarises basic compiler technology. It starts with a short description of the first microprocessor architecture followed by a review of major hardware design changes to improve its performance. These changes are possibly due to the advances in semiconductor technology and the gradually increasing number of transistors on the chip. Pipelined superscalar processors with out-of-order execution to exploit instruction level parallelism are discussed. The evolution of memory design to improve the speed of data access is further presented and various cache designs to exploit program locality are described. Finally, basic program compilation and optimisation methods are discussed.

### 2.1 Processor architecture

It is important to know the architecture of the platform in order to effectively optimise programs so that all platform specific features are used in the best possible way. Therefore, this section describes the architecture of the modern processors used in this thesis and presents the major techniques used to improve their performance. It briefly surveys processor evolution and describes pipelining and parallel out-of-order execution of instructions.

#### 2.1.1 Processor design evolution

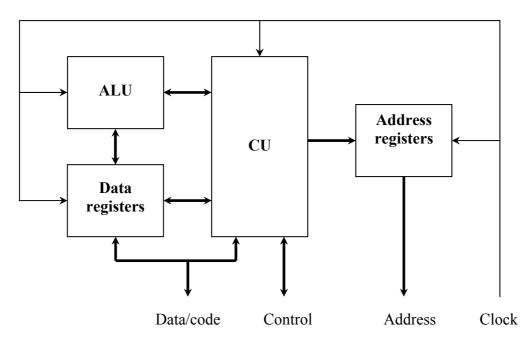

The history of microprocessors dates back to 1971 when the world's first microprocessor, the Intel 4004, was introduced [FHM<sup>+</sup>96]. The major difference between this processor and other computing devices was that all its components were assembled on a single semiconductor chip. The design of this processor is shown in figure 2.1. It is based on the von Neumann architecture [BGN63] that uses the same storage for both data and instructions, fetching and executing instructions one by

Figure 2.1: Von Neumann processor architecture

one. It consists of registers that contain temporal data and memory addresses, a functional unit or ALU (arithmetic and logic unit) that performs mathematical operations and a CU (control unit) that fetches an instruction, decodes it according to the instruction set and controls its execution. Typically, instruction execution in a von Neumann processor occurs in five stages: fetching the instruction, decoding the instruction, loading data from memory or register, performing an operation and storing the result in a register or memory. Thin arrows in figure 2.1 show the propagation of the synchronisation clock signal. Thick arrows in this figure represent wide bus connections consisting of more then one signal that interconnect all processor components. The processor also communicates with external devices such as memory using external data/code, control and address buses.

The Intel 4004 has a simple design by today's measures. It processes data in 4 bits, has sixteen 4-bit general-purpose registers, can address up to 4 KB of data memory and has a clock speed of 108 KHz. Nevertheless, most of its components can still be found in current mainstream SISD (single instruction single data) computing systems, according to Flynn's computer architecture classification [Fly72]. Other types of computing systems such as SIMD (single instruction multiple data) and MIMD (multiple instruction multiple data) are used in parallel machines

and surveyed in [Dun90], however, they are beyond the scope of this thesis. SISD computers are further classified by their instruction set. If they support a large number of complex instructions covering as many operations as possible, they are called CISC (complex instruction set computer) computers. If they support a minimal instruction set covering only the most commonly used instructions, they are called RISC (reduced instruction set computer) computers. Differences between these architectures are described further in section 2.1.2.

Since the introduction of the first microprocessor, all further design changes have been to improve the processor performance due to the ever-increasing demand for faster data processing. A relatively straightforward way to speed up a processor is to make transistors, which are the basic blocks of the chip, smaller and faster, enabling more transistors to be placed on the single chip and increasing the processor clock speed. One of the Intel's founders, Gordon Moore, made a prediction in 1965 that the number of transistors on the chip would double every 18 months [Moo65]. This prediction, referred to as Moore's law, has been surprisingly accurate: while Intel's 4004 microprocessor had 2300 transistors and had a clock speed of 108 kHz, today's processors may have hundreds of millions of transistors on a chip and can operate at gigahertz frequencies such as Intel's Itanium 2, for example [MN03]. Furthermore, this allows the speeding up of the processor by increasing the processor data width and by enabling the addition of full integer and floating-point arithmetic.

Research on increasing the chip density continues. However, it faces many obstacles. One of the major problems is that current designs are approaching the physical limit of semiconductors where classical physics laws are no longer applicable and quantum effects are to be considered, as shown in [Llo00] and [Fra02]. Therefore, promising technologies such as nano and molecular ones are being developed [Lun02], [BDG02]. Another key problem of current semiconductor technology is the increase in the chip power dissipation that has grown from just a few watts in the first microprocessors to more than one hundred watts for some processors such as the Intel Itanium 2 [Int03a], for example. This power is dissipated as heat and requires special cooling systems. Otherwise, the processor may become inoperable or can even be physically destroyed. Thus, a new research direction in the area of low power electronics has appeared, aimed at designing power aware

computer architectures to reduce power consumption. Major methodologies of the low power design are introduced in the book [RP96].

#### 2.1.2 Pipelining

The previous section described those advances in semiconductor technology that allow the placing of large amounts of transistors on a chip and make it possible to explore different designs to speed up microprocessors. Burger and Goodman present speculations in [BG97] about various potential processor designs when a one billion transistor chip is available. However, the scope of this thesis is mainstream SISD processors. Therefore, the following sections present design changes to extend and speed up von-Neumann architecture microprocessors.

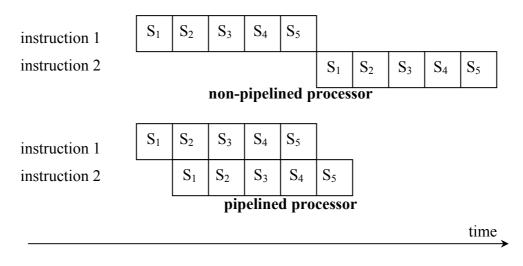

One of the most significant changes in processor design came from the understanding that the execution of instructions can be overlapped in time. This potential for overlapping instructions is called ILP (instruction-level parallelism). One of the first techniques to exploit ILP comes from the observation that instruction execution stages in von-Neumann architectures, described in the previous section, are potentially independent for different instructions. The technique for overlapping the execution of different stages of instructions is called pipelining [RL77]. This name appeared due to the analogy with pipelines when a continuous stream of instructions passes the processor and each part of the processor simultaneously executes different stages of different instruction in the stream. Figure 2.2 demonstrates this technique and shows the execution of two instructions on non-pipelined and pipelined processors with five abstract execution stages.

This technique was first implemented in the IBM's Stretch computer in 1959 as described in [Blo59]. However, implementing a pipeline in the first CISC microprocessors had been problematic due to the variable number of cycles for each instruction execution [HP96]. RISC architectures overcome this problem. These architectures and their advantages over CISC architectures are presented in [PD80]. Briefly, RISC architectures have a minimal instruction set consisting of the most commonly used instructions and simplified hardware that enables pipeline implementation, optimised for the fastest possible execution with a reduced number of cycles per instruction. The first implementations consisted of five main stages

Figure 2.2: Instruction execution on non-pipelined and pipelined processors

[HP96]: fetching, decoding, instruction execution, accessing memory and writing data back to register, variations of which can still be found in most of the current processors. One of the costs for such architectures is a more complex programming target, unlike CISC processors where the complex instruction set is aimed at easing programming. This resulted in the development of special automatic compiler techniques described in section 2.3.

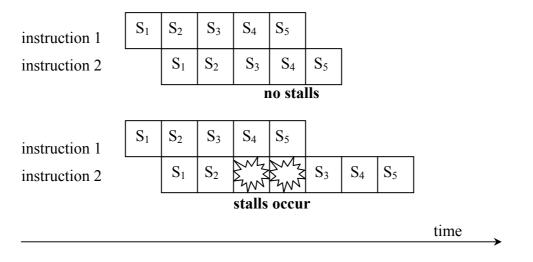

One of the main problems that degrade the high potential performance of pipelined processors happens when the instruction is stalled in the pipeline and so are all the following instructions. This situation is called a hazard and may occur in three cases [HP96]. The first hazard type is called data hazard and arises when one of the instructions in the pipeline depends on the results of a previous instruction. In this case, the execution of this instruction has to be delayed until the dependence is resolved. Figure 2.3 shows an example of the behaviour of the pipeline when the abstract stage S<sub>3</sub> of the second instruction depends on the results of the first instruction. Three possible types of data dependences exist in this hazard [RL77]. A RAW (read after write) dependence arises when an instruction attempts to read from a source before an earlier instruction writes into it so that it gets an old value. It is often referred to as a true dependence. A WAR (write after read) dependence arises when an instruction writes to a source before an earlier instruction reads it so that the earlier instruction gets a new value. A WAW (write after write) dependence arises when an instruction writes to a source before an earlier instruction writes into it so that the earlier instruction writes to a source before an earlier instruction reads it so that the earlier instruction writes to a source before an earlier instruction writes instruction reads it so that the earlier instruction writes to a source before an earlier instruction writes into it so that the earlier instruction writes to a source before an earlier instruction reads it so that the earlier instruction writes to a source before an earlier instruction writes into it so that the earlier instruction writes to a source before an earlier instruction writes into it so that the earlier instruction writes to a source before an earlier instruction writes into it so that the earlier instruction writes to a source before an earlier instruction writes into it so that the ear

Figure 2.3: Instruction execution on a pipeline when stall occurs

that writes are performed out of order. WAR dependencies are often referred to as anti-dependencies and WAW ones as output dependencies. It is possible to minimise data hazard stalls or even eliminate some of them on a hardware level by a forwarding technique, when the result of the current instruction is forwarded immediately to all processor units that may potentially need it [HP96]. Another way to reduce data stalls is by better instruction scheduling to improve pipeline performance as shown in section 2.3.

The second hazard type is called structural hazard and occurs when the same processor functional unit such as the ALU is used in more than one stage of the pipeline and several instructions need it at the same time. This may happen when for example the ALU is used for both data and address calculations. In this case, two subsequent instructions that have some data calculations and memory access may attempt to use the ALU at the same pipeline stages that will cause a stall. However, it can be solved by duplicating the functional units to allow all possible combinations of instructions in the pipeline without structural hazard stalls and is based on the trade-off between the cost and the speed of the processor.

The last hazard type is called a control hazard and arises in branch instructions, when a decision has to be made as to whether or not to take the branch, but the information on which it is based is not yet available. One of the simplest solutions to cope with this problem is to continue fetching instructions after the branch and if the branch is taken, all the fetched instructions are cleared and the fetch is restarted from the new address. However, if the branch is always taken, the pipeline will be always flushed after this instruction, thus, considerably degrading performance. To prevent such situations, a branch prediction table is used. It stores information about whether the particular branch was taken or not so that when this instruction is executed again, the processor will continue executing the instruction in the pipeline from the predicted address. Nevertheless, it can be potentially problematic to predict the outcome of the branch on the first occurrence or when the condition for the branch changes frequently. In this case, software methods for program analysis and branch prediction are used in cooperation with hardware methods. It is shown in section 2.3 and chapter 3.

One of the measures of how well the instructions are overlapped is CPI (clock cycles per instruction). It can be used to analyse the effectiveness of the pipeline for the particular program. Ideally, if all data and control stalls are eliminated it is possible to achieve the maximum performance of one cycle per instruction. However, further potential improvement in performance is possible by fetching more than one instruction in parallel and is discussed in the following section.

### 2.1.3 Superscalar processors

The CPI of the pipelined microprocessor is always limited by 1. However, it is possible to further improve performance if the microprocessor has the capability of issuing more than one instruction simultaneously and execute them in parallel. In this case, the CPI is not limited and can be far less then 1. Processors that have a pipelined architecture but are enhanced with a multiple-issue capability, are called superscalar microprocessors and described in detail in books [Joh91] and [HP96]. The straightforward design change to enable pipelined processors executing instructions in parallel would be to duplicate functional units and to add issue logic to fetch two or more instructions simultaneously. However, the main challenge in the design of the superscalar processor is to cope with those instructions that have dependencies without stalling the processor.

Instruction dependencies are classified into three types. The first type called "data dependencies" occurs when simultaneously issued instructions are data dependent and therefore cannot be executed in parallel. It corresponds to the RAW

data dependence in the processor pipeline. The second type called "name dependencies" or "storage conflicts" arises when the same registers or memory locations are used by simultaneously issued instructions. It corresponds to WAR and WAW data dependencies in the pipeline. The last type called "control dependencies" occurs when there is a branch instruction among simultaneously issued instructions.

The simplest way to cope with these hazards would be to stall the processor until all of them are resolved, however, it can considerably degrade performance. Nevertheless, it is possible to overcome data hazards by better static compiler scheduling, as shown in section 2.3 and chapter 3, or by dynamic scheduling where the processor rearranges the order in which instructions are executed. It enables the processor to look ahead of the instructions with dependence or resource conflicts and execute further independent instructions instead of stalling. This approach is implemented by inserting a buffer called an "instruction window" between the decode and execute stages. In this case, the processor places instructions into this window and then issues those instructions that do not have any dependencies and thus can be executed. This can result in the out of order issue of instructions from the buffer and therefore processors that use this approach are referred to as processors with out-of-order execution.

Overcoming WAR and WAW hazards is possible by providing additional buffers, called reservation stations, that fetch operands of the decoded instructions as soon as they are available, and by renaming the same destination registers with the names of different reservation stations. This technique, called register renaming, can therefore eliminate name dependencies between instructions.

Preventing the processor from stalling on branch instructions can be achieved by using speculation techniques, where the execution of the instructions following the branch continues even if it has not been decided whether this branch is taken. A branch-prediction buffer can assist the speculation by keeping information about whether this branch was taken or not last time. However, if the branch is wrongly predicted during out-of-order instruction execution and the program continues executing, it can generate incorrect results. Therefore, special speculation status bits are attached to instructions and registers. The use of these bits allows the processor to mark all instructions that are executed after the branch, so that if the branch prediction failed, the results of the wrongly executed instructions can be discarded.

Finally, it should be noted, that there are ways, other than superscalar techniques, that can execute instruction in parallel, thus, utilising ILP and improving performance. There are systems consisting of multiple processors, processing vector data, using multi-threading. However, this thesis considers only the mainstream scalar processors where there are two major alternative designs to superscalar microprocessors. These are the VLIW (very long instruction word) approach [Fis83] and the EPIC (explicitly parallel instruction computing) [SR00].

Unlike superscalar processors, where the performance is improved by dynamic rescheduling of instructions, VLIW processors use a single instruction that explicitly specifies several concurrent operations independent from each other. They have a simplified hardware without dynamic scheduling or dependencies resolutions thus relying on compilers and other software methods to pack and schedule instructions. Furthermore, the code produced is generally not portable across different architectures and thus, is not used for general-purpose computing. However, it is popular in DSP (digital signal processing) applications where most of the execution time is spent in small kernels that are relatively easy to analyse for dependencies and to optimise on the assembler level for the specific DSP processor.

The EPIC approach combines some features of VLIW and superscalar processors. It relies on the compiler to extract instruction level parallelism and to schedule independent instructions statically as in the case of VLIW. However, it is also similar to a scalar processor with a sequential instruction set that allows programs to be portable among various processor implementations. This approach is used in Intel's IA-64 processors, as described in [HMR<sup>+</sup>00], [MN03] and [Int03a].

### 2.2 Memory hierarchy

The previous section concentrated on how to improve the processor performance. However, the overall computer performance depends not only on the processor speed but also on the speed of all components. One such component is the memory system. This section describes memory design evolution, locality and cache classifications.

#### 2.2.1 Memory design evolution

Computer memory is used as storage for program code and data. It is one of the key computer components and influences the overall computer performance by taking the burden of supplying data steadily to the microprocessor. The simplest design of the computer system would be if all data is kept and processed in the same non-volatile memory. In practice, however, it is not feasible because permanent memory devices such as tapes or magnetic and optical disks are generally slow. The economical and electronic trade-off in this technology is that it is possible to build fast but small or large but slow memory systems. Therefore, a memory hierarchy, based on speed, size and cost is used. It was first introduced in the Atlas computer that was developed at the University of Manchester [KE62].

A typical memory hierarchy contains registers inside the processor, which are small in number but provide immediate access; reasonably fast and large main memory for storing both program code and data; and finally some slow permanent storage. Scheible surveys various hardware memory designs in [Sch02]. Main memory is often referred to as RAM (random access memory) because any word in such memory can be accessed in random order. There are two basic types of RAM: SRAM (static random access memory) and DRAM (dynamic random access memory). The difference between these two types is in the hardware implementation. Dynamic memory has a simple design and needs to be refreshed periodically so as not to loose data, thus, making this memory cheap but relatively slow. Static memory has a more complex design without the need to be refreshed, thus working faster than DRAM. However, it is physically larger and more expensive. Therefore, DRAM is a common choice for main memory.

Advances in semiconductor technology improve the main memory size and transfer speed by placing more transistors with higher density on the chip. Furthermore, it is also possible to improve DRAM performance by changing memory and interface design. Some of those designs are surveyed in [Sch02]. Briefly, one of the techniques is to make the bus that connects the processor and memory wider so that more data can be sent to the processor within each cycle. Another technique, called interleaving, is based on separating memory into several independent banks and allowing access to multiple data at the same time without

conflicts. Synchronous DRAM (SDRAM) can speed up sequential memory access by matrix interconnection topology. Finally, two recent competing technologies are Rambus DRAM (RDRAM) and Double Data Rate DRAM (DDR DRAM). RDRAM provides a new interface with a packet-based protocol that allows overlapped memory transactions. DDR DRAM uses a technique where data is transferred between processor and memory on both the rising and the falling edges, thus, doubling memory speed without any increase in clock frequency [CJD<sup>+</sup>01].

#### 2.2.2 Locality and cache design

The previous section described advances in the hardware design of main memory to improve its speed. Nevertheless, the gap between processor and memory performance is widening exponentially [HP96]. One of the most commonly used techniques to solve this problem is based on placing small and fast intermediate storage between the main memory and the registers within the processor [Smi82]. This small storage is called cache memory and is used to keep frequently used data and code closer to the processor so that it can access them faster.

Cache memory exploits locality. There are two types of locality – spatial and temporal. Spatial locality means that a memory location adjacent to a referenced location is likely to be referenced soon. Temporal locality means that a memory location recently referenced is likely to be referenced in the nearest future. Whenever the processor requests an item of data from memory, it first checks whether this data can be found in cache. If data is not in cache, a cache miss occurs. In this case, data is fetched from slow main memory to the processor and is simultaneously placed into cache. If the program exhibits temporal locality so that the processor requests the same data later, a cache hit occurs and this data is only fetched from the fast cache, thus, considerably reducing the overall memory access time. To exploit spatial locality, a fixed-size block of adjacent data to the requested data is also fetched from main memory to cache on a cache miss. Therefore, if the processor requests this adjacent data later, it is fetched directly from the cache, speeding up execution of the program.

When data is moved to the cache, the location within the cache is determined by its original address and the cache organisation. The cheapest and simplest organisation is used in direct-mapped caches, where each memory location can be mapped to one unique location in cache using the modulo function:

Address cache = Address main memory MOD Size cache

However, the major drawback of this cache type is the reduced capability for exploiting locality. This happens when new data is fetched to an already allocated place in cache, so that old data has to be replaced even if it can be potentially used in the near future. In contrast, fully associative caches allow data to be placed anywhere in cache. However, this cache organisation is more complex and expensive as the cache now keeps not only the data but also its corresponding address. It needs to have fast logic for finding this data by comparing the requested address with all the stored addresses in the cache simultaneously (associatively). Therefore, due to economical reasons set-associative caches are used. They consist of a number of sets so that the memory location is first mapped to the set using a module function in the same way as direct-mapped caches. Data can then be placed anywhere within the set. If there are *n* possible locations in the set where data can be placed, the cache is called *n*-way set associative. When the set is full, some data should be replaced. Two most commonly used replacement strategies are random, where data is replaced randomly within the set and LRU (least-recently used) strategy, where data accesses are recorded and the least used data is replaced, thus, attempting to exploit temporal locality.

The above methods are used to speed up data reads from memory because in practice they dominate memory access. However, memory writes can also considerably degrade the overall performance. There are two main cache policies for cache behaviour when a data write occurs. The simplest policy is "write through" where data is written to both cache and main memory, however, it usually stalls the processor until the operation is finished. One solution is not to stall the processor by introducing a write buffer that allows overlapping processor execution with writing to memory. Another policy is called "write back". This policy allows data to be written back to the cache without writing it to memory first. Only when this data is to be replaced in cache due to other memory requests, is it written to main memory. This policy better exploits temporal locality, but the cache organisation is more complex and needs to control data synchronisation between cache and main memory.

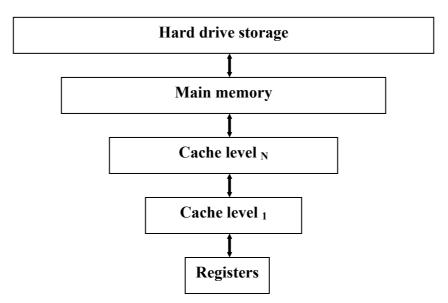

Figure 2.4: Memory hierarchy in current computing systems

Since the gap between processor and memory speed continues to grow and the amount of data to process grows as well, the memory hierarchy continues to alter as shown in figure 2.4. Multilevel caches are introduced to accommodate the increasing gap between the speed of the main memory and the cache, so that the closer the cache is to the processor the smaller and faster it is.

Virtual memory allows the processing of larger amounts of data than the main memory size. It uses main memory as a cache for larger storage such as the hard drive by dividing it into pages so that when the memory access occurs it is mapped to a specific page. If a page is not in memory, a page fault occurs and this page is loaded into the main memory from the hard drive or other storage. Since the cost of a page fault is high due to the access to the relatively slow devices, a fully associative policy is usually used so that pages can be placed anywhere in main memory. When main memory is full, the least recently used page is replaced. To speed up the mapping of physical addresses to virtual addresses, a page table or TLB (translation look-aside buffer) is used. It caches the physical addresses of recently used pages and, thus, provides a fast translation from virtual to physical addresses.

An important characteristic that shows the cost of memory behaviour is the cache miss rate, which is the percentage of the memory accesses that result in cache misses. There are three sources of misses: compulsory, capacity and conflict. Compulsory misses occur when data is brought to the cache for the very first time. Capacity misses occur due to the limited cache size so that when it is full, some data that is still in use nevertheless has to be replaced. Conflict misses occur in direct-mapped or set-associative caches when too many main memory lines are mapped to the same cache set so that some data, later accessed, has to be discarded.

Reducing cache misses means reducing the number of costly accesses to main memory and therefore potentially speeding up the program execution. Many different techniques have been proposed to reduce data traffic between main memory and the cache. Software methods to analyse program behaviour and reduce cache misses are surveyed in chapter 3. Hardware methods are out of the scope of this thesis and the most common of them are described in [HP96]. Briefly, they are based on making the block size larger to bring more data from main memory on the cache miss thus, reducing compulsory misses. Reducing conflict misses is possible by increasing the associativity of the cache or by using different designs such as column-associative caches [AP93], skewed-associative caches [BS95], victim caches or by using randomised cache placement [TG99]. However, it should be noted that while reducing cache miss rate improves the performance of the in-order processors, where each cache miss causes the stall, it does not necessarily improve the performance of current out-of-order execution processors due to the potential overlapping of memory access with executing other instructions instead of stalling. This is examined in detail in chapter 5.

### 2.3 Compiler technology

The compiler is an important software component of any computing system, responsible for translating user program into machine code. This section contains a brief survey of compiler technologies and describes major compiler optimisations to produce faster code for superscalar processors with out-of-order execution, excluding memory optimisations, which are described in chapter 3.

#### 2.3.1 Introduction to compiling

Early computers were programmed directly using binary machine code. However, this process is not only tedious and time consuming, but also requires a good knowledge of the underlying computer hardware. Moreover, binary code is difficult to analyse and modify if any further changes are necessary. Furthermore, such codes are generally not portable to new architectures. Therefore, an assembly language is used instead. It translates program source code containing computer instructions into machine code. The assembler usually has some basic support for data structures and subroutines making it easier to develop and modify programs. However, it still requires knowledge of the particular architecture instruction set and is not portable between different platforms.

This problem has been solved by introducing high-level computer languages and their respective compilers. High-level languages are usually designed for some particular classes of problems and are platform independent allowing programmer to write compact portable programs. Compilers, however, are typically platform dependent and translate programs written on the high-level language into the assembly language or machine code of the targeted architecture. One of the earliest languages and compilers developed for scientific applications was Fortran. It is not only still in use today, but it also became a standard for numerical programs [PTV<sup>+</sup>92]. Fortran compilers use mature technology that has been developed over many years and is now capable of producing high quality fast code for a variety of platforms.

Compilers transform source code into machine code through different stages. The common stages are lexical, syntax and semantic analysis that form the compiler front-end. Code optimisation and machine code generation constitute the compiler back-end. These stages are described in detail in [ASU86].

Briefly, the compiler front-end is responsible for checking that the program is correct lexically, syntactically and semantically. It constructs an abstract intermediate representation of the program. This intermediate representation removes redundancies in the application and contains only unique machine-independent information about the original program. This simplifies the retargeting of the compiler for different languages and platforms so that only the compiler front-end is changed for a new language and the compiler backend is changed for a new platform. The code optimisation stage remains intact. The code optimisation stage is responsible for improving the quality of the intermediate code so that faster and smaller machine code will be produced. This stage will be described in more detail in section 2.3.2 and in chapter 3. Finally, the compiler back-end is responsible for producing assembly or machine code from the program intermediate representation for the target platform. During this stage, registers are allocated and certain platform-specific optimisations, such as instruction scheduling, are performed. It is described in the next section.

#### 2.3.2 Code optimisations

Using high-level languages helps the programmer to abstract from the underlying machine architecture, to have an easier and simpler development process and to write compact portable programs. However, this means that the compiler has a major role in producing fast and efficient target machine code automatically. This is not a trivial task because potentially many variants of the machine code exist for the same program. Hence, the task of the compiler is to find and produce the best version of the machine code for any given program. This process is called program optimisation.

Program optimisations are performed via program transformations that can improve speed and/or size of the final machine code without changing the behaviour and meaning of the program [ASU86]. These transformations are applied at different compiler stages and can either be platform independent, when properties of the targeted machine are not taken into consideration, or platform dependent when various platform parameters are taken into account.

Before optimising any program, the compiler has to perform control flow analysis and data flow analysis. Control flow analysis is usually performed in the front-end of the compiler where the intermediate representation of the program is generated. It divides the whole program into basic blocks that have only one entrance and one exit, and produces a control flow graph that shows how the basic blocks are interconnected. This helps the compiler identify loop structures and other parts of the program that can be further legally transformed. Data flow analysis is performed on the intermediate representation of the program. It examines the flow of data in the whole program, producing information about each variable, such as where this variable is first defined, how it is used in basic blocks and finally where it is redefined. This is a complex process that requires examining all control paths of the program but simplifies further data dependence analysis and program optimisation.

Once the control and data flow graphs are available, the compiler starts optimising the program. First, machine independent optimisations are performed. These include transformations such as code motion, code inlining, common subexpression elimination and copy propagation transformations [ASU86]. Briefly, the code motion transformation moves invariant statements within a loop outside, thus, eliminating redundant computation and speeding up the overall execution of the program. Code inlining is used to remove the call statement overhead by merging small and frequently called subroutines with the caller. This transformation can speed up the program but it can also increase the size of the program if there is more than one place where the subroutine is called. Finally, both global common subexpression elimination and copy propagation are used to avoid repetitive computations, thus, improving code performance as well as code size.

The final compiler stage is to allocate register and memory resources to the program and to generate and schedule machine instructions from the program intermediate representation. It is not a trivial task, as the compiler has to take into account various machine parameters in order to produce the fastest possible code for the particular architecture. This stage is beyond the scope of this thesis and is described in detail in [ASU86] and [GH88].

Briefly, during the register allocation phase, the compiler has to determine which values should be placed in registers based on the data flow and dependence analysis. The major difficulty of this task is that there is a limited number of hardware registers. The main objective is to reduce the number of memory accesses giving a potential performance improvement. Various methods for register allocation are presented in [ASU86] and [Tou02].

During the instruction scheduling phase, the compiler has to produce and optimise the instruction sequence in such a way that data and control dependencies are not violated and that the program's ILP is exploited without introducing processor stalls [SCD<sup>+</sup>97]. Though most modern processors have an automatic support for deriving program ILP at run time, it is limited because the processor can analyse ahead only those instructions that reside in the instruction window at a time. Compilers have the advantage of analysing the whole program and scheduling instructions for the pipeline globally and in some cases predicting branches using static information from the data flow and dependencies analysis. Furthermore, to exploit features of modern superscalar processors with out-of-order execution the compiler can perform various machine dependent optimisations.

Loop unrolling and software pipelining are two major transformations that can improve scheduling of the program and better exploit ILP. Loop unrolling replicates the loop body multiple times, thus, reducing the number of loop branch checks. This is one of the transformations used in the research for this thesis and thus, is reviewed in more detail in chapter 3. Software pipelining transforms a loop in such a way that each instruction of the new loop is assembled from instructions belonging to different iterations of the original loop, thus, allowing the overlapping of multiple instructions without data dependencies. It is described in detail in [BGS94].

One of the difficulties compilers face in this phase is the lack of precise information about the hardware of the targeted machine. Hence, simplified machine models are used that reduce the potential for exploiting ILP. This is discussed in detail in chapter 3.

#### 2.4 Summary

The evolution of the processor design is surveyed in this chapter starting from the description of the internal structure of the world's first microprocessor, the Intel 4004. Advances in the semiconductor technology allowing higher transistor density per chip are discussed and followed by the brief analysis of various design changes to improve the processor performance. CISC and RISC processor architectures are compared and pipelining technique implementation for both architectures are discussed. Multiple issue techniques and out-of-order instruction execution for exploiting instruction level parallelism are presented. This is followed by the discussion of various hazards on superscalar processors that can considerably

degrade the performance and the hardware solutions used to overcome them. The need for memory hierarchy to accommodate the widening gap between the speed of the processor and the memory is outlined. The main memory designs are briefly surveyed, which is then followed by the introduction of caches that exploit locality to further reduce memory access time. The most common cache organisations are analysed. Finally, this chapter finishes with the introduction to the compiling technology and with the description of basic optimisations excluding memory analysis and optimisations that are discussed in the next chapter.

# **Chapter 3**

## **Memory hierarchy optimisations**

This chapter surveys existing work related to the research of this thesis. It reviews various program transformations that can improve memory performance by reducing data traffic between the processor and the memory and primarily focuses on loop tiling, array padding and loop unrolling, though other transformations are also briefly reviewed. It discusses certain program representations and issues concerning the legality of transformations. Various static techniques for analysing data reuse and locality and for obtaining the number of cache misses within a program are further presented. It is followed by a survey of static algorithms for transforming programs to improve data locality and reduce conflict and compulsory misses. A review of program dynamic analysis is then presented. It obtains various run-time parameters that are not available statically by means of profiling or simulations. This run-time information can be used during dynamic optimisations such as in feedback assisted, iterative or adaptive compilation, as described in the last section of this chapter.

### **3.1 Program transformations**

This section describes various transformations and their effect on program performance. This includes major loop and data transformation used in the research of this thesis such as loop tiling, array padding and loop unrolling. Other transformations such as software pipelining and prefetching are also briefly described. Examples of mathematical notations for the representation of loops and arrays to ease dependence analysis and automatic application of those transformations are presented.

#### **3.1.1 Introduction**

The aim of new hardware designs of computing systems that target numerical codes is faster execution of a broad range of programs. Those programs are generally

developed for older platforms that do not reflect new design features, and are ported to a new hardware without major changes due to economical reasons. Therefore, there are two major ways to improve the performance of the unchanged program: by analysing and rescheduling the stream of instructions dynamically by the processor or by analysing and transforming the program statically by the compiler. The first way of scheduling instructions by the processor is limited as the processor can only analyse several instructions at a time and does not see the whole program behaviour as discussed in section 2.3.2. On the contrary, a compiler can analyse the whole program and adapt it to a new computing system using program transformations, even if the original algorithm is unchanged.

The aim of program transformations is to reorder operations in a program to improve performance without changing the meaning of the program. Program transformations that remove redundancies and improve scheduling were first introduced in this thesis in section 2.3.2. This section focuses on memory transformations that are used to overcome the increasing gap between the speed of the processor and the main memory, by improving data locality and minimising the number of non-local memory accesses.

Memory transformations are divided into two groups: loop and data transformations. Loop transformations modify loop iteration order in an attempt to achieve better data locality, without changing the meaning of the original program. The emphasis on loop structures is due to an observation that programs spend most of their execution time in loops. Data transformations modify the layout of array data in the memory with the same aim of achieving better locality.

Bacon et al. [BGS94] survey various loop and data transformations and describe their influence on program locality and performance. This thesis focuses on three transformations: loop tiling, unrolling and array padding. These transformations have been selected due to their potential to considerably improve performance. They are described in detail in the following sections 3.1.2, 3.1.3 and 3.1.4.

Transformations such as loop unrolling and array padding are relatively easy to analyse and implement, while others, such as loop tiling, require thorough dependence analysis and can be difficult to implement inside the automatic optimising compiler. Therefore, linear algebraic models to represent loop and data structures are used to enable automatic optimisations.

One of the first significant papers that uses a mathematical model to unify various transformations is [WL91b] by Wolf and Lam. It describes a matrix model for transformations and incorporates dependence vectors to check the validity of transformations within the same framework. It provides the theory for the automatic analysis of the validity of standalone or even compound transformations and enables the data locality analysis, as is shown in further sections of this chapter. However, the loop transformation theory of this paper is limited by unimodular transformations such as loop interchange, reversal and skewing for the perfectly nested loops.

Briefly, this model represents a loop nest as a finite convex polyhedron and each iteration in this loop nest is described as an index vector  $\vec{\mathbf{p}}$ . Data dependencies restrain the execution order of the iterations and can be represented as dependence vectors  $\vec{\mathbf{d}}$ . Loop transformations map original iterations into new ones and can be represented as matrices  $\mathbf{T}$ . When loop transformation is applied, new iteration and dependence vector is found as the matrix-vector multiplication, that is  $\vec{\mathbf{p}}_{new} = \mathbf{T}\vec{\mathbf{d}}$ . If a compound transformation, consisting of several transformations  $\mathbf{T}_1, \mathbf{T}_2, \dots, \mathbf{T}_N$  has to be applied, the final matrix of the compound transformation is found as a consecutive multiplication of all matrices  $\mathbf{T}_{new} = \mathbf{T}_1\mathbf{T}_2...\mathbf{T}_N$ . Finally, a new transformation is legal if the transformed code can be executed sequentially, or in mathematical terms, if all transformed dependence vectors are lexicographically positive. The definition of a lexicographically positive vector  $\vec{\mathbf{d}}$  is the following: if  $\exists i: (d_i < 0$  and  $\forall j < i: d_j \ge 0)$ .

The following example, taken from [WL91b], demonstrates the use of the loop transformation theory:

for

$$I_1$$

: = 1 to N do

for  $I_2$ : = 1 to N do

$a[I_1, I_2] := f(a[I_1, I_2], a[I_1+1, I_2-1]);$

The dependence vector of this double nested loop is (1,-1) and the iteration vector is (i, j). Consider that in the first case the loop interchange transformation has to be applied and in the second case a compound transformation consisting of the loop

interchange and the loop reversal transformations has to be applied. The matrix of the loop interchange transformation is  $\mathbf{T} = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$  and the matrix of the loop reversal transformation is  $\mathbf{T} = \begin{bmatrix} -1 & 0 \\ 0 & 1 \end{bmatrix}$ . When loop interchange is applied, the new dependence vector  $\mathbf{d}_{new} = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ -1 \end{bmatrix} = \begin{bmatrix} -1 \\ 1 \end{bmatrix}$  is lexicographically negative. Therefore, this transformation is not legal for this code. However, when the compound transformation of the loop interchange and the loop reversal is applied, the new dependence vector  $\mathbf{d}_{new} = \begin{bmatrix} -1 & 0 \\ 0 & 1 \end{bmatrix} \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ -1 \end{bmatrix} = \begin{bmatrix} 0 & -1 \\ 1 & 0 \end{bmatrix} \begin{bmatrix} 1 \\ -1 \end{bmatrix} = \begin{bmatrix} 1 \\ 1 \end{bmatrix}$  is lexicographically positive. Hence, this compound transformation can be legally applied to the above code.

Analysing data dependencies for large programs can be a complex and slow process and can be hard to implement inside a production compiler. The Banerjee test [Ban88], based on the Intermediate Value Theorem, is commonly used to detect all the dependencies between variables within a given region of the program. A faster method for determining data dependence relationships based on an integer programming algorithm is introduced by Pugh in [Pug91]. To speed up the analysis, an Omega test is used. This method allows one to determine if an integer solution exists to a set of linear equalities and inequalities.

Another important issue, which arises after applying some particular transformations, such as loop tiling, is that loop bounds have to be transformed as well. Calculating new loop bounds can be performed directly by transforming all inequalities derived from the loop nest, as proposed originally by Wolf and Lam in [WL91b]. However, it may potentially contain excessive maxima and minima computations in the new loop bounds that can degrade overall performance. To overcome this problem, Ancourt and Irigoin introduce several algorithms in [AI91] that optimise minima and maxima computations in the loop bounds using integer linear system methods.

Li and Pingali extend unimodular transformation theory in [LP92] by using nonsingular matrices for transformations. In this loop transformation framework called

|            | do $x_l = L_l$ , $U_l$                    |

|------------|-------------------------------------------|

| $S_{1a}$ : | $H_{1a}\left( x_{l} ight)$                |

|            | do $x_2 = L_2$ , $U_2$                    |

| $S_{2a}$ : | $H_{2a}\left( x_{1}	ext{ , } x_{2} ight)$ |

|            |                                           |

|            | <b>do</b> $x_n = L_n$ , $U_n$             |

| $S_n$ :    | $H_n(x_1,\ldots,x_n)$                     |